Designing Deterministic

High-Performance Computers

As system or software architects, strive to build reliable and predictable systems. An important part of this endeavor is ensuring deterministic behavior, something that is essential for safety, availability, and meeting end-to-end timing guarantees.

However, this task is becoming increasingly challenging with the move to high-performance computing (HPC) within the automotive industry. In contrast to traditional systems using the AUTOSAR Classic Platform, things are substantially more complicated with HPC systems using AUTOSAR Adaptive Platform based on QNX or Linux.

Some of the key differences are:

- No statically defined tasks – instead, we have a multitude of processes, some known in advance, others generated by the system, all of which can dynamically create threads.

- Lots of thread interaction – calling threads sit waiting for their syscall or communication to complete, resulting in rescheduling as threads enter and leave their waiting state.

- Lots of parallelism – today’s system-on-chip (SoC) devices execute many threads on a range of heterogeneous cores and specialized accelerators.

Because of these differences, HPC systems are very hard to model in the manner we have traditionally used. But this doesn’t mean it can’t be done. We simply need to adapt our models to a level of detail more fitting to this new technology.

Thus, the goal is no longer to model every last element influencing the real scheduling behavior. Instead, our goal is to generate a model representing the system’s overall behavior. This ensures that planning is still possible while providing insights into deterministic behavior.

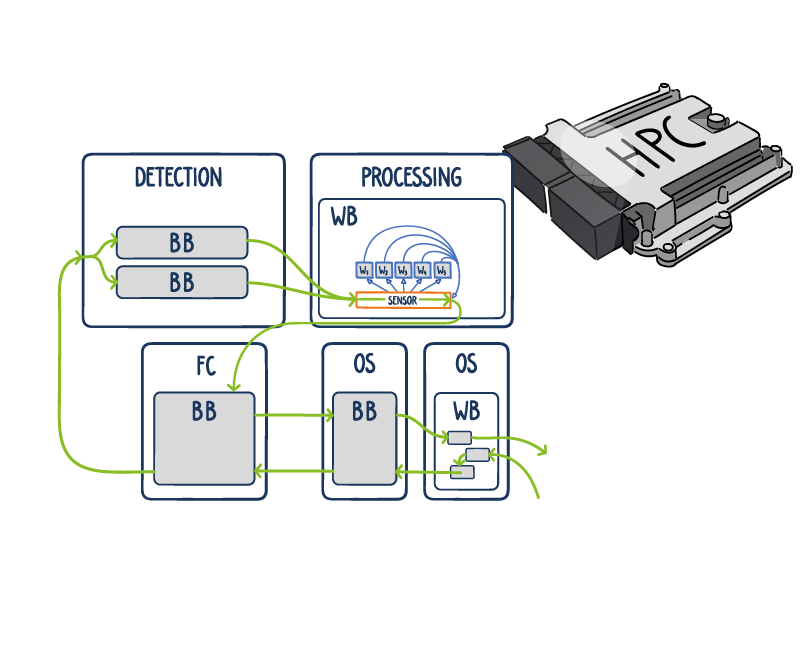

One proven method is using a black box/white box modeling concept. Both boxes represent a function or unique set of work to be done:

- Black box – describes a function’s necessary execution time and its inherent parallelism.

- White box – provides additional details as needed for a more refined model, such as detailing every thread created, its execution time, and its memory needs.

This combination of black and white boxes is then mapped onto the HPC system and triggered accordingly (periodic, data-driven, or event). They are also used as building blocks for event chains.

This allows the system or software architects to analyze their system’s real-time and end-to-end performance, such as evaluating timing from sensor to actuator under a range of possible conditions.

If you’d like to learn more about how INCHRON can support you in developing your HPC, feel free to contact us using the form below.

Any questions?

Feel free to contact us.